��λ�߶Δ��a�܄ӑB�@ʾ�·���OӋ

һ�� ���Ŀ��

1�� �˽┵�a�ܵĹ���ԭ����

2�� �W���߶Δ��a���@ʾ�g�a�����OӋ��

3���W��VHDL��CASE�Z�估���Ӵ��OӋ������

���� ���ԭ��

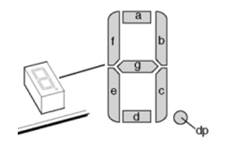

�߶Δ��a��������_�l�^���г��õ�ݔ���@ʾ�O�䡣�ڌ��ϵ�y��ʹ�õ��ǃɂ���λһ�w����ꎘO���߶Δ��a�ܡ�����o�B���a�����D4-4-1��ʾ��

�D4-1 �o�B�߶Δ��a��

�����߶Δ��a�ܹ������B�ӵ�GND����ꎘO�ͣ��������a�ܵ��е���һ���α�ݔ����ƽ���t�������@һ�α��c������֮�t��������ꖘO�ԵĔ��a���c֮��ô����λһ�w���߶Δ��a���چ��o�B���a�ܵĻ��A�ϼ����������x����һλ���a�ܵ�λ�x��̖�˿ڡ��˂����a�ܵ�a��b��c��d��e��f��g��h��dp���B����һ��8�����a�ܷքe�ɸ��Ե�λ�x��̖�����ƣ����xͨ�Ĕ��a���@ʾ�����������P�]��

���� ������

�����Ҫ����ɵ��΄����ڕr���̖�������£�ͨ�^ݔ����Iֵ�ڔ��a�����@ʾ�������Iֵ���ڌ���Еr�����֕r��x��1024HZ�������r犣����Ă��܄��_�P����ݔ�룬���Ă��܄��_�P�Þ�һ�����M�Ɣ��r���ڔ��a�����@ʾ��ʮ���M�Ƶ�ֵ��

�ġ� ���E

1�� ���_QUARTUSIIܛ�����½�һ�����̡�

2�� ���깤��֮�����½�һ��VHDL File�����_VHDL������Ԓ��

3�� ���Ռ��ԭ�����Լ����뷨����VHDL�����ھ���VHDL�����Ñ��Ʌ��չ�P���ṩ��ʾ������

4�� ������VHDL�����������������ͬ���һ��

5�� ���Լ�������VHDL�����M�о��g�����棬��������e�`�M���ġ�

6�� ���g����o�`�����Ñ��Լ���Ҫ���M�й��_���䡣������ɺ����M��ȫ���gһ�Σ���ʹ���_������Ч��

7�� �����������Ì�����������_�����FPGA���_�c������ģ�K�B��������

������{�õı����ṩ��VHDL���a���t����B�����£�

CLK��FPGA�r���̖���Ӕ��֕r�CLOCK3�������@�M�r��O��1464HZ��

KEY[3..0]�����a���@ʾݔ����̖���քe�ӓ܄��_�P��K4��K3��K2��K1��

LEDAG[6..0]�����a���@ʾ��̖���Ӕ��a�ܵ�G��F��E��D��C��B��A��

SEL[2..0]�����a�ܵ�λ�x��̖���Ӕ��a�ܵ�SEL2��SEL1��SEL0��

8�� �����d��|ͨ�^JTAG�ڌ�������sof�ļ����d��FPGA�С��^�쌍�Y���Ƿ��c�Լ��ľ���˼��һ�¡�

�塢 ���F���c�Y��

���OӋ�ą���ʾ�����������OӋ�ļ����d��Ŀ�������_�J��̖�B�Ӿ������_�B�ӣ���������̖Դģ�K�ĕr��x���1464HZ���܄���λ�܄��_�P��ʹ���һ����ֵ���t�˂����a�ܾ��@ʾ�܄��_�P����ʾ��ʮ���M�Ƶ�ֵ��

���� �����

1�� �L�����沨�Σ������f����

2�� ������r�����ι����ģ���׃����r犕���ʲô׃����

3�� ���ԭ�����OӋ�^�̡����g���沨�κͷ����Y����Ӳ���yԇ�Y��ӛ�����