�����������ͬ��ʹ�ܵļӷ�Ӌ����

һ�� ���Ŀ��

1�� �˽���M��Ӌ�����Ĺ���ԭ����

2�� �Mһ����ϤQUARTUSIIܛ����ʹ�÷�����VHDLݔ�롣

3���r��ھ����^���е����á�

���� ���ԭ��

���M��Ӌ�����Б�����ࡢ������ȫ��Ӌ����֮һ�������������ͬ��ʹ�ܵļӷ�Ӌ�����ľ��w�����^�����£�

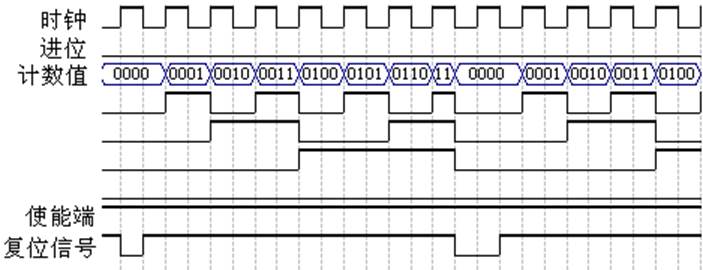

�ڕr������ص���r�£��z�yʹ�ܶ��Ƿ����SӋ����������SӋ�������xʹ�ܶ˸��ƽ��Ч���t�_ʼӋ������tһֱ�z�yʹ�ܶ���̖����Ӌ���^�����ٙz�y��λ��̖�Ƿ���Ч�����ƽ��Ч��������λ��̖�����Õr��ʹӋ��ֵ���㣬�^�m�M�Йz�y��Ӌ�����乤���r����D4-3-1��ʾ��

�D4-3-1 Ӌ�����Ĺ����r��

���� ������

�����Ҫ����ɵ��΄����ڕr���̖�������£�ͨ�^ʹ�ܶ˺͏�λ��̖����ɼӷ�Ӌ������Ӌ��������Еr���̖ʹ�Ô��֕r�Դģ�K��1HZ��̖����һλ�܄��_�PK1��ʾʹ�ܶ���̖���Ï�λ�_�PRST��ʾ��λ��̖����LEDģ�K��D1��D4����ʾӋ���Ķ��M�ƽY�������LED����ʾ������λ��‘1’��LED���ʾ������λ��‘0’��ͨ�^ݔ�벻ͬ��ֵģ�MӋ�����Ĺ����r���^��Ӌ���ĽY����

�ġ� ���E

1�� ���_QUARTUSIIܛ�����½�һ�����̡�

2�� ���깤��֮�����½�һ��VHDL File�����_VHDL������Ԓ��

3�� ���Ռ��ԭ�����Լ����뷨����VHDL�����ھ���VHDL�����Ñ��Ʌ��չ�P���ṩ��ʾ������

4�� ������VHDL�����������������ͬ���һ��

5�� ���Լ�������VHDL�����M�о��g�����棬��������e�`�M���ġ�

6�� ���g����o�`�����Ñ��Լ���Ҫ���M�й��_���䡣������ɺ����M��ȫ���gһ�Σ���ʹ���_������Ч��

7�� �����������Ì�����������_�����FPGA���_�c������ģ�K�B��������

������{�õı����ṩ��VHDL���a���t����B�����£�

CLK��FPGA�r���̖���Ӕ��֕r�CLOCK4�������@�M�r��O��1HZ��

Ret��Ӌ����λ��̖���Ӻ��İ尴�I�_�PRST��

EN��Ӌ��ʹ����̖����һ���܄��_�PK1��LOCK KEY AREA����

CQ��Ӌ���Mλ��̖����һ��LED��D8��LED AREA����

COUT��Ӌ��ݔ�������Ă��B�m��LED��D1-D4��LED AREA����

8�� �����d��|ͨ�^JTAG�ڌ�������sof�ļ����d��FPGA�С��^�쌍�Y���Ƿ��c�Լ��ľ���˼��һ�¡�

�塢 ���F���c�Y��

���OӋ�ą���ʾ�����������OӋ�ļ����d��Ŀ�������_�J��̖�B�Ӿ������_�B�ӣ���������̖Դ�ĕr��x���1HZ��ʹ�܄��_�PK1�Þ���ƽ��ʹ�܄��_�P���ϣ�����λLED�����Ռ��ԭ�������α��c�������ӷ����ӵ�9�r��D8���Mλ��̖�����c��������λ�I�����İ��ϵ�RST�I�����º�Ӌ�������㡣����܄��_�PK1�Þ���ƽ���܄��_�P���£��t�ӷ�����������

���� �����

1�� �L�����沨�Σ������f����

2�� ������VHDL�����^������Ҫ�f����Ҏ�t��

3�� �����ԭ�����OӋ�^�̡����g���沨�κͷ����Y����Ӳ���yԇ�Y��ӛ�����

4����׃�r��l�ʣ������F�����ʲô��׃��ԇ����@һ�F��