|

|

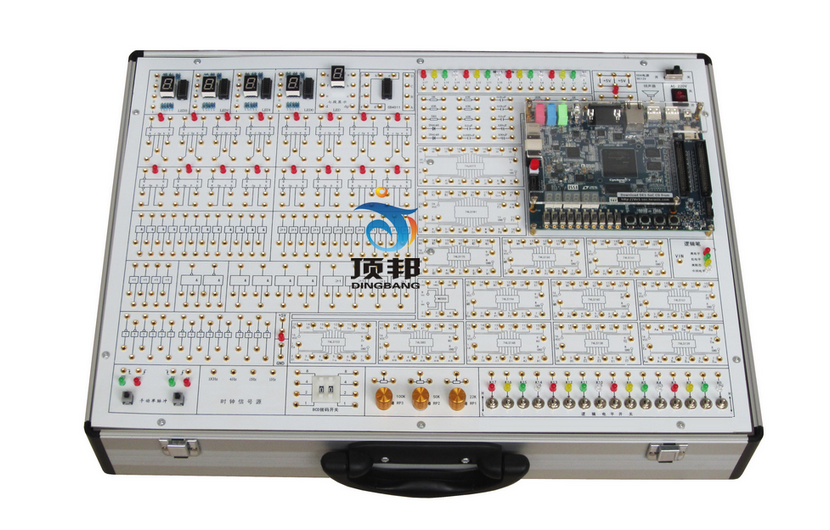

������ʾ��

1��؛Ʒ��գ��w����؛�rՈ�z�锵��ϵ�y���ƽ�_��؛Ʒ���^���ˌ�����ϵ�y���ƽ�_�Ĕ��������������̎���ܓp��B�Ĕ���ϵ�y���ƽ�_��

2���|����픰���w���ṩ����ϵ�y���ƽ�_�aƷ�f�����ȵ��|���l�����|���ڣ����|���������ṩ������ϵ�y���ƽ�_�����M�S�ޣ������l�����Z�r�ṩ������ϵ�y���ƽ�_���Ѓ��S�ޣ�

3���˓Q؛���w�η���ԭ���µĔ���ϵ�y���ƽ�_�x���e�`����ϵ�y���ƽ�_ُ�I�����e�`����ɔ���ϵ�y���ƽ�_���˓Q؛Ҫ���������ܣ�

4��؛�ڣ�����ϵ�y���ƽ�_�İl؛�ڞ酢��ֵ��������Ҫ�˽┵��ϵ�y���ƽ�_�ľ��_؛�ڣ�Ո�c픰���N���ˆTϵ��

5�����w������ϵ�y���ƽ�_���κ��Ɇ���Ո��늣�021-36334717 ���҂����Ɍ��I��ʿ�����ṩ���P����ϵ�y���ƽ�_����ԃ��

�Ҳ������ҵĮaƷ?Ո�c���aƷ����� |