��(sh��)���l��Ӌ���O(sh��)Ӌ

һ�� ���?z��i)��?/strong>1�� �˽�Ⱦ��Ȝy�l�ķ�����ԭ����

2�� ���������FPGA��(n��i)���O(sh��)Ӌ��N����ģ�K��

3�� ����VHDL�ڜy��ģ�K�O(sh��)Ӌ����ļ��ɡ�

���� ���ԭ��

���^�l�ʾ�����������̖�چ�λ�r�g��1s����(n��i)׃���ĴΔ�(sh��)������һ���r�g�g��T��Ҳ�Q�l�T�r�g����(n��i)�y���@����������̖���؏�(f��)׃���Δ�(sh��)��N���t���l�ʿɱ�ʾ��

f��N/T

������ı�ʾʽ���Կ��������r�g�g��Tȡ1s���tf��N�������l�T����ʼ�ͽY(ji��)���ĕr�̌�����̖���f���S�C�ģ�������һ���}�_���ڵ������`��Mһ�������y����(zh��n)�_�ȣ��O(sh��)���y��̖�}�_���ڞ�Tx���l�ʞ�Fx����(d��ng)�y���r�g��T=1s�r���y����(zh��n)�_�Ȟ�δ=Tx/T=1/Fx���ɴ˿�֪�@�Nֱ�Ӝy�l���Ĝy����(zh��n)�_���c���y��̖���l�����P(gu��n)����(d��ng)���y��̖�l���^�ߕr���y����(zh��n)�_��Ҳ�^�ߣ���֮�y����(zh��n)�_���^�͡���ˣ��@�Nֱ�Ӝy�l��ֻ�m�Ϝy���l���^�ߵ���̖�����ܝM���������y���l��(n��i)�Ĝy�����ȱ��ֲ�׃��Ҫ����Ҫ�õ��������y���l��(n��i)�Ĝy�����ȱ��ֲ�׃��Ҫ��(y��ng)ԓ���]�������l�ʜy��������������

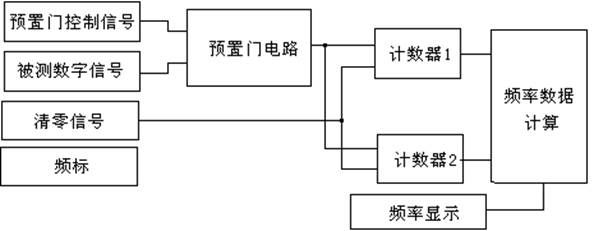

�Ⱦ����l�ʜy�l�Č��F(xi��n)�����������ÈD4-19-1��ʾ�Ŀ�D�팍�F(xi��n)��

�D4-19-1 �Ⱦ��Ȝy�l���F(xi��n)��D

���^�Ⱦ�����ָԓ�l��Ӌ�����y���������l��(n��i)�������Ɍ��F(xi��n)��ͬ���ȵĜy�������y�������c�l�ʟo�P(gu��n)���D���A(y��)���T��̖ͨ����1s�����(n��i)������һ��ͬ���T�·���Á팍�F(xi��n)���y�l��(bi��o)�c���y�l�ʵ�ͬ������ߜy�����ȣ��p�ٻ����`�ԓ�����c�����}�_�f(xi��)�{(di��o)�����Á����ƃɂ�Ӌ��(sh��)���Ć����}�_��Ӌ��(sh��)��1��Ӌ��(sh��)��2�քe�Á��o�l��(bi��o)�ͱ��y��(sh��)���}�_Ӌ��(sh��)���O(sh��)��ͬ���T���ƽY(ji��)���rӋ��(sh��)��1Ӌ��(sh��)N1��Ӌ��(sh��)��2Ӌ��(sh��)N2�����O(sh��)�l��(bi��o)�l�ʞ�F1�����y�l��λFx���t�Ɍ�����ʽ��

Fx/N2=F1/N1��…………………��1��

Fx����F1/N1��* N2……………��2��

�ɹ�ʽ���Կ������y�������c�A(y��)���T�r�g�o�P(gu��n)����Ҫ��F1���l�ʷ�(w��n)���ȁ��_�������Ԟ�����ߜy�����ȣ���Ҫ������l��(bi��o)���l�ʷ�(w��n)���ȣ��Q��Ԓ�f���y�����Ȼ����Ͻ������l��(bi��o)�ķ�(w��n)���ȣ����l��(bi��o)�ķ�(w��n)����λ10��6���t�y���`��߅���_��10��6����ԓ�·�У����˴_���l��(bi��o)Ӌ��(sh��)�c���y�l����ȫͬ���������y�l�ʵ��������_ʼӋ��(sh��)��1s�Ժ��y�l�ʵ�������ֹͣӋ��(sh��)����ͬ���T����ɱ��y��̖�����ƣ��O(sh��)Ӌ������N���ӣ����ɌW(xu��)��������ɡ�

��������ֱ�Ӝy�l���M���l�ʜy�����l�T�r�g�̶���1s���l�T��̖��һ��0.5Hz�ķ��������l�T��Ч�����ƽ�����g����ݔ����}�_�M��Ӌ��(sh��)�����l�T��̖���½��ؕr�̣����殔(d��ng)ǰ��Ӌ��(sh��)ֵ�������������е��l��Ӌ��(sh��)���������l�T�r�g��1s��0.5Hz�������������@ʾ���l����1s犸���һ�Σ����@ʾ�ă�(n��i)�����l�T�½��ؕr�i���ֵ��

����l�T�r�g�҂��O(sh��)����1s�������@�N�l��Ӌ�H�ܜy���l�ʴ��ڻ��ߵ���1Hz����r�����l��Խ�ߣ�����ҲԽ�ߡ����H��(y��ng)���У��l��Ӌ���l�T�r�g�ǂ���׃������(d��ng)�l��С��1Hz�ǣ��l�T�r�g��Ҫ�m��(d��ng)�Ŵ���һ����(bi��o)��(zh��n)�ĕr犣��چ�λ�r�g��(n��i)�磺0.1�댦���y��̖���}�_�M��Ӌ��(sh��)��������̖���l�ʡ�

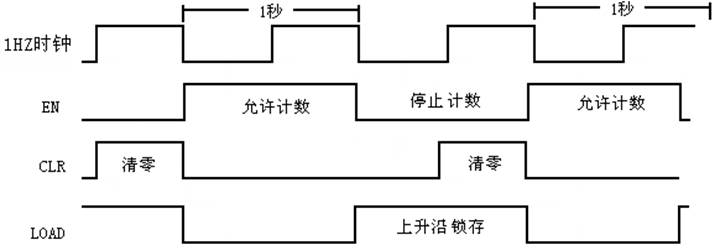

���O(sh��)Ӌ�l��Ӌ�ĕr�˂��߶δa���������@ʾ99,999,999Hz��������O(sh��)Ӌ�r���ð˂�4λ���M�ƴa��BCD�a������ʾ������߀�����ͬ�ӵİ˂�4λ���M�ƴa�팦ݔ����l���M��Ӌ��(sh��)�����l�T�½��صĕr�����ߵ�ֵ�i�浽�Ĵ����С�����̖�ĕr���P(gu��n)ϵ���D4-19-2��ʾ��

�D4-19-2 ������̖�r���P(gu��n)ϵ

���� ����(n��i)��

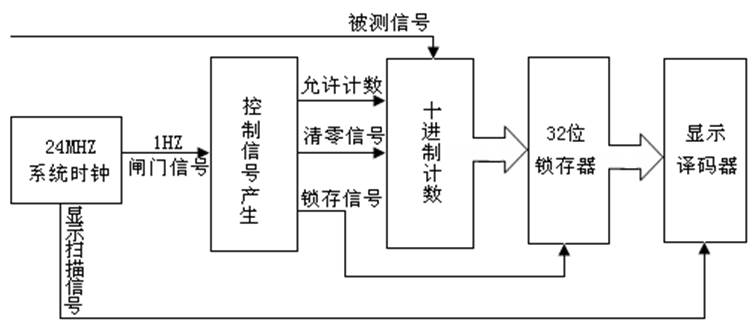

�����Ҫ��ɵ��΄�(w��)�����O(sh��)Ӌһ���l��Ӌ��ϵ�y(t��ng)�r��x��24MHZ�ĕr犣��l�T�r�g��1s��ͨ�^��ϵ�y(t��ng)�r��M�з��l�õ��������l�T����ƽ���g����ݔ����l���M��Ӌ��(sh��)����(d��ng)�l�T׃�͵ĕr��ӛ䛮�(d��ng)ǰ���l��ֵ�������l��Ӌ��(sh��)�����㣬�l�ʵ��@ʾÿ�^2��ˢ��һ�Ρ��䌍�F(xi��n)��D���D4-19-3��ʾ��

�D4-19-3 �y�l���F(xi��n)��D

�ġ� ���E

1�����_QUARTUSIIܛ�����½�һ�����̡�

2�����깤��֮�����½�һ��VHDL File�����_VHDL������Ԓ��

3�����Ռ��ԭ�����Լ����뷨����VHDL�����ھ���VHDL�����Ñ��Ʌ��չ�P���ṩ��ʾ������ʾ�������ṩ6��VHDLԴ����ÿһ��Դ�������һ���Ĺ��ܡ�����w�Ĺ������±�4-19-1��

| �ļ����Q | ��ɹ��� |

| CLKOUT.VHD | �a(ch��n)��1HZ���l�T��̖���@ʾ������̖ |

| TELTCL.VHD | �ڕr犵����������ɜy�l�Ŀ�����̖�� |

| CNT10.VHD | ʮ�M��Ӌ��(sh��)�����ڌ����ʹ��8�����M��Ӌ��(sh��) |

| SEG32B.VHD | 32λ���i���������i�������̖�������£���Ӌ��(sh��)��ֵ�i�� |

| DISPLAY.VHDL | �@ʾ�g�a�����i��Ĕ�(sh��)��(j��)�@ʾ������ |

4��������VHDL�����������������ͬ���һ��

5�����Լ�������VHDL�����M�о��g������ģ�K��̖�ļ�������������e�`�M���ģ���K���г���ͨ�^���g������ģ�K��̖�ļ�������w����Ո���Ռ������

6���½�һ���D�ξ��ļ����������ɵ�ģ�K��̖�ļ��������У�������(j��)Ҫ��߅��������

7�����Լ����õĵij����M�о��g���棬����������e�`�M���ģ���Kͨ�^���g��

8�����g����o�`����(j��)�Ñ��Լ���Ҫ���M�й��_���䡣������ɺ����M��ȫ���gһ�Σ���ʹ���_������Ч��

9������(j��)����(n��i)���Ì�(d��o)����������_�����FPGA���_�c����(y��ng)��ģ�K�B��������

������{(di��o)�õı����ṩ��VHDL���a���t����B�����£�

CLK��FPGA�r犣��Ӕ�(sh��)�֕r�CLOCK1���������O(sh��)��24MHZ��

CLKIN:���y�l��ݔ����̖�����Խӕr�Դ�������r犡�

LEDAG[6..0]���Ӕ�(sh��)�a�ܵ�A��B��C��D��E��F��G��

SEL[2..0]���Ӕ�(sh��)�a�ܵ�SEL2��SEL1��SEL0��

10�������d��|ͨ�^JTAG�ڌ�����(y��ng)��sof�ļ����d��FPGA�С��^�쌍�Y(ji��)���Ƿ��c�Լ��ľ���˼��һ�¡�

�塢 ���Y(ji��)���c�F(xi��n)��

���O(sh��)Ӌ�ą���ʾ����������(d��ng)�O(sh��)Ӌ�ļ����d��Ŀ��(bi��o)�����ı��y�l��ݔ��˿�ݔ��һ���r���̖���@�r�ڔ�(sh��)�a�����@ʾ�@���r���̖���l��ֵ������׃��(sh��)����̖Դ�ĕr犣����@ʾ��ֵ�Ƿ��c��(bi��o)ֵһ�¡�

���� �����

1�� �L�����沨�Σ������f����

2�� ����(j��)ǰ���B�ĵȾ����l��Ӌ�Č��F(xi��n)�����������Ⱦ����l��Ӌ��VHDL���a��

3�� �����ԭ�����O(sh��)Ӌ�^�̡����g���沨�κͷ����Y(ji��)����Ӳ���yԇ�Y(ji��)��ӛ�����