PS2�ӿ��I�P�@ʾ���

һ�� ���Ŀ��1���W����FPGA�OӋ����ͨ�Ņf�h�ķ�����

2���W��PS2�Ĺ���ԭ��������a��ASCII�a���D�Q��

3������VHDL�����е�һЩС���ɡ�

���� ���ԭ��

PS2ͨ�Ņf�h��һ�N�p��ͬ������ͨѸ�f�h��ͨѸ�ăɶ�ͨ�^CLOCK���r���̖�ˣ�ͬ������ͨ�^DATA�������˿ڣ����Q�������κ�һ�������Ҫ��������һ����ͨѸ�r��ֻ��Ҫ��CLOCK�������ƽ��

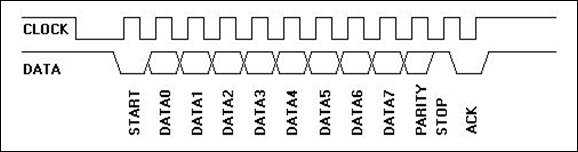

PS2�˜ʣ�Ҏ��ÿ�P������ݔ������ʼλ(start bit)������a(scan code)����ͬλ�z��(odd parity)���Լ��Kֹλ(stop bit)��Ӌ11λ�������p���Д�����ݔ�ķ�ʽ���_��ͨ�ŵ�Ŀ�ġ��Ү����C��(host)��ęC��(slave)���o���ͻ���Ք����r��������ݔ�˿ڼ��l�ʾ���������λ���D4-17-1��ʾ��ÿһ�P������ݔ������֮�������£�

1. ��ʼλ(“0”)

2. 8λ�������ȵĒ���a( scan code )��

3. ��ͬλ�z�飬ʹ����a�c��ͬλ������1�Ĕ��֞��攵����

4. �Kֹλ(“1”)

�D4-17-1 PS2 ���Ђ�ݔ�˜�

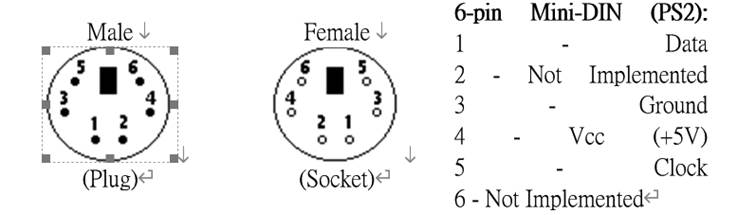

�D4-17-2 PS2 �˿��_λ���x

PS2���ƽӿڃHʹ�õ��ɗl��ݔ�˿ڣ�һ���l�ʶ˿ڣ���һ�t�锵���˿���D4-17-2��ʾ���Ҵ˂�ݔ���؞����B(Tri-State)�������p��(bidirectional)���ԡ�PS2 ��ݔ�aƷ�ϣ���Ҋ������c�I�P�����ߵ���ԭ������ͬ���H����a(scan code)��ͬ������҂���PS2�I�P�����M���f����

�I�P�䌍����һ�����͵İ��I��ꇣ������ɰ��b���·���ϵ�̎����������“�I�P���a��”�����Oҕ�����mȻ��ͬ���I�P���ܲ��ò�ͬ��̎����������������ɵ��΄ն���һ�ӵģ����Oҕ��Щ���I�����£���Щ���I��ጷ��ˣ������@Щ��Ϣ���͵����C������б�Ҫ��̎����̎�����е�ȥ���ӣ���������16�ֹ��ľ��_�^�マ�_���������C�˰�����һ��“�I�P������”�c�I�P̎�����M��ͨӍ������a�����I�P̎��������Ϣ��Ȼ�����ϵ�y��ǰ���I������̎�����顣���C�c�I�P֮�g��ͨӍ���f����IBM�ąf�h��

�I�P̎�������M�ܶ��r�g������Oҕ���I��ꇡ�����l�F�а��I���¡�ጷŻ��L�����I�P�Ͱl��“����a”����Ϣ�����C������a�ЃɷN��ͬ����ͣ�“ͨ�a”��“��a”����һ���I������ȥ���L���ĕr���I�P�Ͱl��ͨ�a����һ���I��ጷŵĕr���I�P�Ͱl�͔�a��ÿ���I�P��������Ψһ��ͨ�a�͔�a���@�����Cͨ�^����Ψһ�Ē���a�Ϳ��Դ_�����Ă����I�����»�ጷš�ÿ���Iһ����ͨ��a�M����“����a��”���F�����е��I�P�����õڶ��ג���a�����ڛ]��һ�����εĹ�ʽ����Ӌ�����a������Ҫ֪��ij���ض����I��ͨ�a�͔�a��ֻ�ܲ��ò���ķ������@�á���Ҫ�eע����ǣ����I��ͨ�aֵ��ʾ�I�P�ϵ�һ�����I��������ʾӡˢ�ڰ��I�ϵ��ǂ��ַ����@����ζ��ͨ�a��ASCII�a֮�g�]���κ��P��

���⣬�ڶ���ͨ�a��ֻ��һ���ֹ�������Ҳ���ٔ�“�Uչ���I”��ͨ�a�ǃ��ֹ������ֹ������@a�ĵ�һ���ֹ�����0xE0���cͨ�aһ�ӣ�ÿ�����I��ጷŵĕr���I�P�͕��l��һ����a��ÿ���IҲ�������Լ���Ψһ�Ĕ�a�����^�c�ҵ��ǣ���a�c��a֮�g��������Ȼ��ϵ�������ڶ��ה�a�Ѓɂ����L�������ĵ�һ���ֹ���0xF0���ڶ����ֹ����nj������I��ͨ�a���Uչ���I�Ĕ�aͨ���������ֹ���ǰ�ɂ��ֹ�0xE0��0xF0�����һ���ֹ����@�����Iͨ�a�����һ���ֹ�����4-17-1�г����I�P���I��ͨ�a�͔�a��

| �Iֵ | ͨ�a | ��a | �Iֵ | ͨ�a | ��a | �Iֵ | ͨ�a | ��a |

| A | 1C | F0,1C | 9 | 46 | F0,46 | [ | 54 | F0,54 |

| B | 32 | F0,32 | ` | 0E | F0,0E | INSERT | 67 | F0,67 |

| C | 21 | F0,21 | - | 4E | F0,4E | HOME | 6E | F0,6E |

| D | 23 | F0,23 | = | 55 | F0,55 | PG UP | 6F | F0,6F |

| E | 24 | F0,24 | \ | 5C | F0,5C | DELETE | 64 | F0,64 |

| F | 2B | F0,2B | BKSP | 66 | F0,66 | END | 65 | F0,65 |

| G | 34 | F0,34 | SPACE | 29 | F0,29 | PG DN | 6D | F0,6D |

| H | 33 | F0,33 | TAB | 0D | F0,0D | U ARROW | 63 | F0,63 |

| I | 43 | F0,48 | CAPS | 14 | F0,14 | L ARROW | 61 | F0,61 |

| J | 3B | F0,3B | L SHFT | 12 | F0,12 | D ARROW | 60 | F0,60 |

| K | 42 | F0,42 | L CTRL | 11 | F0,11 | R ARROW | 6A | F0,6A |

| L | 4B | F0,4B | L WIN | 8B | F0,8B | NUM | 76 | F0,76 |

| M | 3A | F0,3A | L ALT | 19 | F0,19 | KP / | 4A | F0,4A |

| N | 31 | F0,31 | R SHFT | 59 | F0,59 | KP * | 7E | F0,7E |

| O | 44 | F0,44 | R CTRL | 58 | F0,58 | KP - | 4E | F0,4E |

| P | 4D | F0,4D | R WIN | 8C | F0,8C | KP + | 7C | F0,7C |

| Q | 15 | F0,15 | R ALT | 39 | F0,39 | KP EN | 79 | F0,79 |

| R | 2D | F0,2D | APPS | 8D | F0,8D | KP . | 71 | F0,71 |

| S | 1B | F0,1B | ENTER | 5A | F0,5A | KP 0 | 70 | F0,70 |

| T | 2C | F0,2C | ESC | 08 | F0,08 | KP 1 | 69 | F0,69 |

| U | 3C | F0,3C | F1 | 07 | F0,07 | KP 2 | 72 | F0,72 |

| V | 2A | F0,2A | F2 | 0F | F0,0F | KP 3 | 7A | F0,7A |

| W | 1D | F0,1D | F3 | 17 | F0,17 | KP 4 | 6B | F0,6B |

| X | 22 | F0,22 | F4 | 1F | F0,1F | KP 5 | 73 | F0,73 |

| Y | 35 | F0,35 | F5 | 27 | F0,27 | KP 6 | 74 | F0,74 |

| Z | 1A | F0,1A | F6 | 2F | F0,2F | KP 7 | 6C | F0,6C |

| 0 | 45 | F0,45 | F7 | 37 | F0,37 | KP 8 | 75 | F0,75 |

| 1 | 16 | F0,16 | F8 | 3F | F0,3F | KP 9 | 7D | F0,7D |

| 2 | 1E | F0,1E | F9 | 47 | F0,47 | ] | 5B | F0,5B |

| 3 | 26 | F0,26 | F10 | 4F | F0,4F | ; | 4C | F0,4C |

| 4 | 25 | F0,25 | F11 | 56 | F0,56 | ' | 52 | F0,52 |

| 5 | 2E | F0,2E | F12 | 5E | F0,5E | , | 41 | F0,41 |

| 6 | 36 | F0,36 |

PRNT SCRN |

57 | F0,57 | . | 49 | F0,49 |

| 7 | 3D | F0,3D | SCROLL | 5F | F0,5F | / | 4A | F0,4A |

| 8 | 3E | F0,3E | PAUSE | 62 | F0,62 |

��4-17-1PS2 �I�P����a

���� ������

�������΄վ�������PS2�ӿڌ��I�P���I��ͨ�a�ڔ��a�����@ʾ������

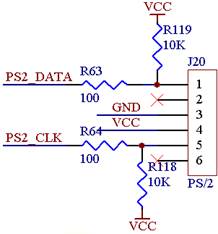

��������õ�PS2�I�P�ӿ��cFPGA�Ľӿ��·��D4-17-3��ʾ��

�D4-17-3 PS2�I�P�ӿ��·�D

�ġ� ���E

1�����_QUARTUSIIܛ�����½�һ�����̡�

2�����깤��֮�����½�һ��VHDL File�����_VHDL������Ԓ��

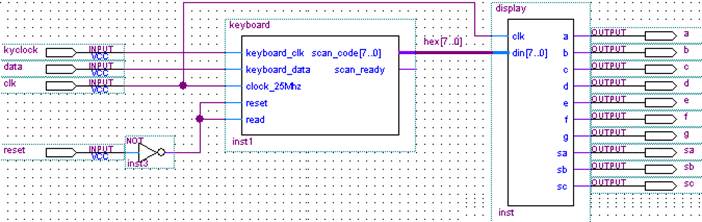

3�����Ռ��ԭ�����Լ����뷨����VHDL�����ھ���VHDL�����Ñ��Ʌ��չ�P���ṩ��ʾ������ʾ�������ṩ2��VHDLԴ����ÿһ��Դ�������һ���Ĺ��ܡ�����w�Ĺ������±�4-17-2��ʾ��

| �ļ����Q | ��ɹ��� |

| keyboard.VHD | PS2�I�P�������·�OӋ�� |

| DISPLAY.VHD | �߶��@ʾ���g�a�·�OӋ�� |

4��������VHDL�����������������ͬ���һ��

5�����Լ�������VHDL�����M�о��g������ģ�K��̖�ļ�������������e�`�M���ģ���K���г���ͨ�^���g������ģ�K��̖�ļ�������w����Ո���Ռ������

6���½�һ���D�ξ��ļ����������ɵ�ģ�K��̖�ļ��������У�������Ҫ��߅����������ɺ����D4-17-4��ʾ��

�D21-4 ���õĈD���OӋ�ļ�

7�����Լ����õĵij����M�о��g���棬����������e�`�M���ģ���Kͨ�^���g��

8�����g����o�`�����Ñ��Լ���Ҫ���M�й��_���䡣������ɺ����M��ȫ���gһ�Σ���ʹ���_������Ч��

9�������������Ì�����������_�����FPGA���_�c������ģ�K�B��������

������{�õı����ṩ��VHDL���a���t����B�����£�

CLK�� FPGA�r犣��Ӕ��֕r�COLCK1�������O��24M��

DATA��PS2�ӿ�DATA��̖����PS2�ӿ�KDA�˿ڡ�

KYCLOCK��PS2�ӿ�CLK��̖����PS2�ӿ�KCL�˿ڡ�

RESET����λ��̖���Ӻ��İ��λ���IRST��

A��B��C��D��E��F��G�����߶δa�@ʾ�^��A��B��C��D��E��F��G

SA��SB��SC�����߶δa�@ʾ�^��SEL0��SEL1��SEL2��

10�������d��|ͨ�^JTAG�ڌ�������sof�ļ����d��FPGA�С��^�쌍�Y���Ƿ��c�Լ��ľ���˼��һ�¡�

�塢 ���Y���c�F��

���OӋ�ą���ʾ����������PS2�ӿڵ��I�P����PS2�ӿڃȡ����OӋ�ļ����d��Ŀ��������������̖Դģ�K�ĕr��x���24MHZ������PS2�I�P�ϵ��I���t�ڌ��ƽ�_�İ�λ���a���ϵ����g��λ���@ʾ�����I�Ē���a���^���䰴�µ��Iֵ�������Ē���a�Ƿ��c��4-17-1һһ���������º��İ��ϵď�λ���IRST�tֹͣ���I�P�Ē��裬���a���ϵĒ���a�����l����׃��

���� �����

1���L�����沨�Σ������f����

2�������ԭ�����OӋ�^�̡����g���沨�κͷ����Y����Ӳ���yԇ�Y��ӛ�����