2.1FPGA�̌W���ϵ�yϵ�y�YԴ

FPGA�̌W���ϵ�y�ǻ���Altera CycloneIV�������_�l��һ���߉��FPGA�������_�lƽ�_�������Ԟ��_�l�ˆT�ṩ�����YԴ�� ����Altera CycloneIVEP4CE6E22C8N FPGA�ĺ��İ�

����Altera CycloneIVEP4CE6E22C8N FPGA�ĺ��İ� 8λ�Ñ��Զ��x���I�_�P

8λ�Ñ��Զ��x���I�_�P 8λ�Ñ��Զ��x�܄��_�P

8λ�Ñ��Զ��x�܄��_�P 8λ�Ñ��Զ��xLED���@ʾ

8λ�Ñ��Զ��xLED���@ʾ 4X4����I�Pݔ��

4X4����I�Pݔ�� 8λ�߶Δ��a���@ʾ

8λ�߶Δ��a���@ʾ 16X16����c��@ʾ

16X16����c��@ʾ 1602LCD�ַ�Һ���@ʾ

1602LCD�ַ�Һ���@ʾ 12864LCD�cꇈD���@ʾҺ����

12864LCD�cꇈD���@ʾҺ���� ����ͨ������ģ�K

����ͨ������ģ�K �������ģ�Mģ�K

�������ģ�Mģ�K ֱ��늙C���D�ٜy�ٿ���ģ�K

ֱ��늙C���D�ٜy�ٿ���ģ�K ���M늙C����ģ�K

���M늙C����ģ�K 8λ���и���ADC�D�Qģ�K

8λ���и���ADC�D�Qģ�K 2·8λ���ٲ���DAC�D�Qģ�K

2·8λ���ٲ���DAC�D�Qģ�K ����/���Q���ӿ�ģ�K

����/���Q���ӿ�ģ�K VGA���ƽӿ�ģ�K

VGA���ƽӿ�ģ�K 2·���нӿ�ģ�K

2·���нӿ�ģ�K PS2���/�I�P����ģ�K

PS2���/�I�P����ģ�K �Դ����ģ�K

�Դ����ģ�K2.2FPGA�̌W���ϵ�yϵ�y����

FPGA�̌W���ϵ�y���ڽ��^�L���Ñ�����Y��Ŀǰ�������Լ����H������Ҫ��ͬ�r������T�W���Լ��Y���_�l���̎��đ���������аl�ġ����YԴ���ԣ����ѽ����w�˻��Aģ�K�������ģ�K��ͨ�����Ƭ�C���Ƶȷ���ă��ݡ�

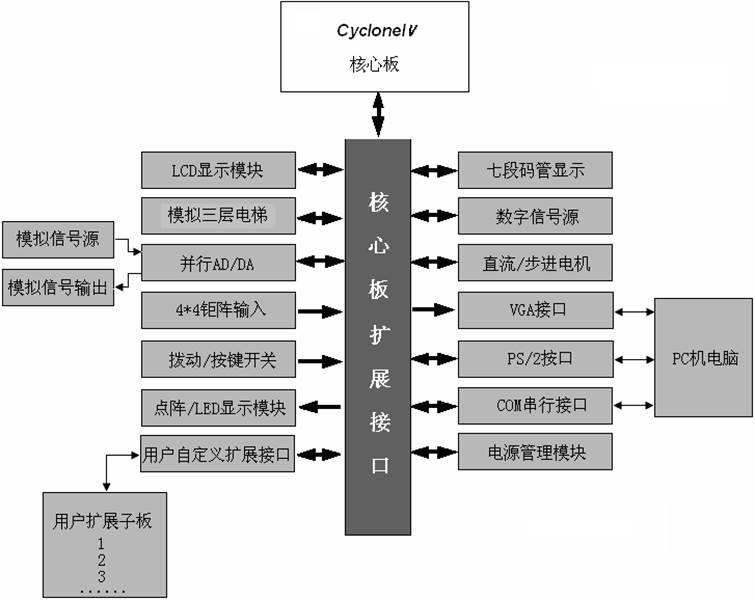

�D2-1FPGA�̌W���ϵ�y���ܿ�D

���������c��B�_�lϵ�y���еĽM��ģ�K��ģ�K�����·���λ���Լ���ģ�K��ϵ�y����������á�

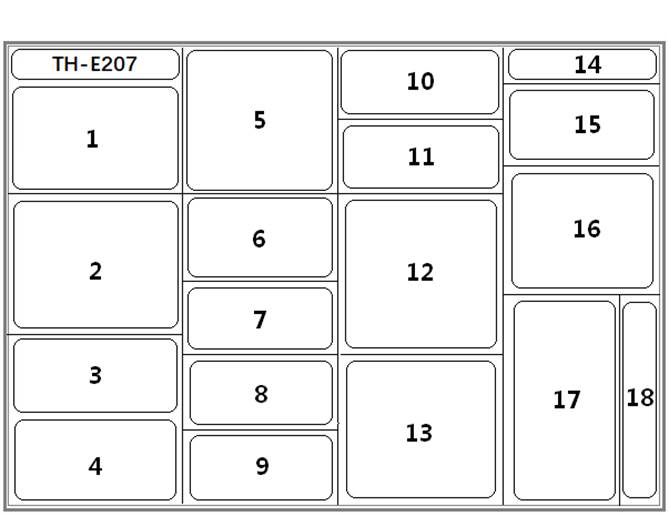

�D2-2FPGA�̌W���ϵ�yģ�K�M�ɿ�D

| ģ�Kλ�� | ���Q | �������� |

| 2 | Cyclone IVFPGA | ��оƬEP4CE6E22C8N���İ� |

| ݔ���@ʾģ�K | ||

| 15 | ��λ�߶Δ��a�� | ������λһ�w�Ĺ�ꎸt�߶Δ��a�܃ɂ��M�ɰ�λ�߶Δ��a���@ʾģ�K�����ڌ���Д��˵��@ʾ�� |

| 7 | ��λLED�� | �tɫLED�������ڶ��M�Ɣ������@ʾ |

| 17 | 16X16�����c� | 16X16�cꇡ�ݔ�����εĈD�Σ�ͨ�^�B�m���ƿ��@ʾֱ�^�ĄӑBЧ���� |

| 1 | 12864�D���c�LCD | �ṩ128*64�D�λ��c�ʽҺ���@ʾ |

| 16 | 1602�ַ���LCD | �����ַ��@ʾʹ�� |

| �Ñ�ݔ��ģ�K | ||

| 8 | �܄��_�P | �ܱ��ָߵ��ƽ��ͨ�^�քӿ��ƞ�ϵ�y�ṩ������߉��̖�� |

| 9 | ���I�_�P | �������i���ܵİ��I��ͨ�^�քӿ��ƞ�ϵ�y�ṩ�}�_��̖�� |

| 13 | 4X4����I�P | 4×4�I�P��Ҫ��ͨ�^���̌��F0��F��ݔ�룬Ҳ��������һ�������I�� |

| �ӿ��YԴ | ||

| 16 | VGA�ӿ� | ͨ�^���̌��FVGA�@ʾݔ�� |

| 18 | PS/2�ӿ� | ����ˡ��I�P�����ڶ��ߵĿ��� |

| ���нӿ� | �ṩ2·�B��PC�C�Ĵ��пڣ�����PC�C�c���ϵ�y�Ĕ�����ݔ | |

| 3 | ��̖Դ�ӿ� | �������M�ж༉���l����ͬ�r�ṩ�ĽM��ͬ�l�ʵķ�����̖��ʹ�����x�á�ͬ�r�ṩ���ȡ��l�ȿ��{��ģ�M��̖Դ������ģ�Kʹ�á� |

| ����ģ�K��Ԫ | ||

| 5 | ֱ��늙C | �ṩһ·�ٶȿɿء��ɜy��ֱ��늙Cģ�K |

| ���M늙C | �ṩһ·����λ���M��С7.5�Ȳ��M늙C | |

| ����/���Q�� | ͨ�^����ݔ�벻ͬ�l�ʵ���̖�l | |

| 4 | ADC�D�Q | �ṩһ��8ͨ��8λ����ADC�D�Qģ�K |

| 10 | DAC�D�Q | 8λD/A�D�QоƬ�����FD/A���ܣ�ͨ�^��������B�m���ƿɌ��F��ͬ����ݔ�� |

| 11 | DAC�D�Q | 8λD/A�D�QоƬ�����FD/A���ܣ�ͨ�^��������B�m���ƿɌ��F��ͬ����ݔ�� |

| 6 | ��ͨ�� | 12���t�S�G����ͨ����ʽ���У�������ͨ�������_���⌍� |

| 12 | �������ģ�M | ģ�M������ݵ��_�P�T��Ո����̖�� |

2.3 FPGA���İ�ģ�K�f��

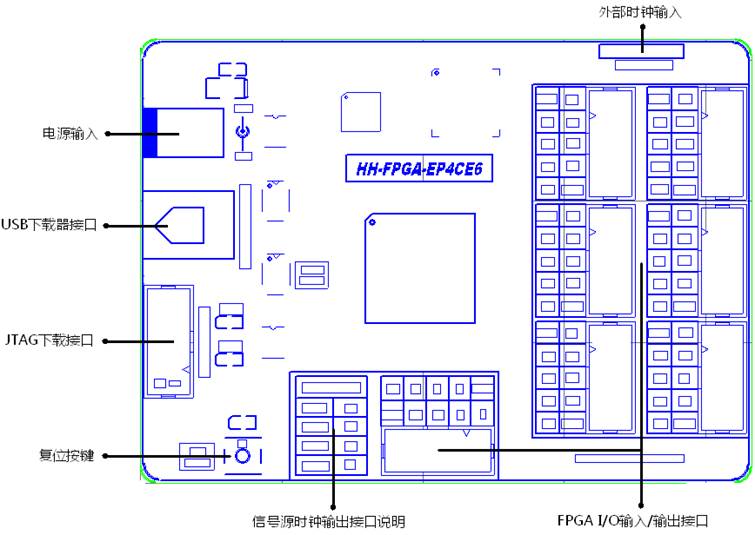

���������c��B���İ����еĽM��ģ�K��ģ�K�����·���λ���Լ���ģ�K��ϵ�y����������á�

HH-FPGA-EP4CE6���İ壨����D��

�D2-3���İ�ģ�Kλ�ÈD

| ���İ�λ̖ | ���Q | �������� |

| U2 | CycloneIV | ��оƬEP4CE6E22C8N |

| �{ԇ�ӿ� | ||

| JP8 | JTAG�{ԇ�ӿ� | JTAG���Ñ����dFPGA���a�����d����оƬ���a�����r�{ԇNios II CPU���Լ��\��Quartus II�ṩ��Ƕ��ʽ߉�����xSignalTap II�ȣ� |

| J2 | USB�{ԇ�ӿ� | ���dUSB-BLASTER�{ԇ�����ܣ� |

| �惦��Ԫ | ||

| U8 | SDRAM | 8Mbytes SDRAM |

| U1 | EPCS4 | 4 Mbits���Ӵ����������� |

| ݔ��/ݔ���O�� | ||

| U4 | ���� | �߾���50MHz�r�Դ���Ñ�������FPGA�Ȳ�PLL����l�����õ������l�ʵĕr� |

| S1 | ��λ���I | ԓ���I���{ԇNios II CPU�r�����������λ��̖����ȻҲ�������Ñ��Զ��x����������ݔ�� |

| �Uչ�ӿ� | ||

| JP1-JP7 | 10оFPGA I/Oݔ��ݔ������ | �ṩ�߂�2.54mm�˜��g���ʮо�ӿڹ��Ñ�Ϊ�ʹ�� |

| �Դ | ||

| J1 | ֱ���Դݔ�� | ֱ���Դ�m�����������m����Ҫ���+5V/1A |

| U3-U7 | �Դ���� | ؓ؟�ṩ���������5V��3.3V��2.5V��1.2V늉� |

���挦���ϵĸ���ģ�K����Ӳ���B����Ԕ���f����

2.3.1Cyclone IV EP4CE6E22C8N

HH-FPGA-EP4CE6���İ��ϲ��õ�FPGA��Altera Cyclone IV EP4CE6E22C8N���@��FPGA���YԴ�������¡� 6��272 LEs��߉��Ԫ��

6��272 LEs��߉��Ԫ�� 270K total RAM bits

270K total RAM bits 15 Embedded multipliers��18×18Ӳ���˷�����

15 Embedded multipliers��18×18Ӳ���˷����� 2PLLs���i��h��

2PLLs���i��h�� 91User I/O pins��������I/O��

91User I/O pins��������I/O�� Fineline PGFP144-pin package�����b��

Fineline PGFP144-pin package�����b��2.3.2JTAG�{ԇ�ӿ�

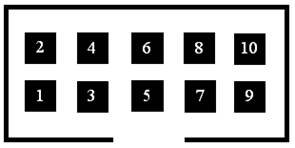

HH-FPGA-EP4CE6���İ����A����JTAG�ӿڹ��Ñ����d���a��JTAG�ӿڼȿ��Ԯ������İ�FPGA���{ԇ/���̽ӿڣ�Ҳ�������ڌ������������M�о��̡����İ����ṩJTAG�{ԇ�ӿڞ����D2-4��ʾ��10ᘲ�������ÿ����ᘵ���̖���xҊ��2-3��

��2-3JTAG������̖���x

ע�� ‘/’��ʾԓ��ᘛ]���κ���̖��

2.3.3USB�{ԇ���d�ӿ�

HH-FPGA-EP4CE6���İ���dUSB���d�{ԇ�����Ñ�ֻ��Ҫһ��USB-B�B�Ӿ����Ɍ��F������{ԇ�ͼ��d��2.3.4�惦��Ԫģ�K

FPGA����оƬEPCS4����ʹ�õ�����оƬ��Altera��˾���a�Ĵ�����������оƬEPCS4S08��Altera��˾�Ĵ������������ǘI����̓r����������������ܰ�����ϵ�y���̣�ISP�������Ͷ�ξ����������@�N���ʹ���������������Cyclone™FPGA�����ڴ������̓r�����I��������a�䣬ʹ��FPGA������������Y�ϣ��ṩһ�N�M������̓r��������Ŀɾ���Ƭ��ϵ�y��SOPC����Q������EPCS4SI8N��������̖���R�c�������2-4��ʾ��

��3-3EPCS4��������

�����İ匦������оƬEPCS4�M�о��̿���ͨ�^���·�����

�þ�����|ͨ�^���İ��ϵ�JTAG�{ԇ�ӿڣ���QuartusII���g���ɵČ�������������.Jic�ļ��M�����þ��̡�

SDRAM�惦ģ�K

���İ��SDRAM��һƬ3.3Vͬ���ӑBRAM������4M×16bits�Ĵ惦���g�����ٶ�SDRAM�ߎ����������������C��Nios II CPU���Թ����ڷdz���Ч�Ġ�B��

2.3.5ݔ��/ݔ���O��

�������İ����ṩ�˸߾��ȡ��߷�����50MHz�r犣�ԓ�r�ֱ���cFPGA��PIN-23��GCLK0�����_���B��

����OӋ�ˆT��Ҫ�����l�ʕr�Դ��������FPGA�Ȳ��M�з��l������FPGA�Ȳ�PLL���l��;�����õ���

����I

�_�l������һ����λ���I��λ�ں��İ�����½ǡ���λ���I�����LED���λָʾ������λ���I���r�����ƽ����LED����

��λ���I�B�ӵ�FPGA��PIN_24���_�ϣ����Թ��_�l�ˆT����Nios II CPU�ď�λ��̖����ȻҲ����������ͨ�İ��I��ʹ�á�